Memory

- Circular Dependency

- Delayed lines

- Odd ticks

- Bit Inverter

- Bit Switch

- Input Selector

- The Bus

- Saving Gracefully

- Saving Bytes

- Counter

- Little Box

Circular Dependency

Задача: Создайте "круговую зависимость". Это схема, в которой вход компонента зависит от его собственного выхода.

В такой ситуации невозможно определить выход компонента, потому что сперва нужно определить вход, который сам ависит от выхода, образуя петлю.

A → B → C

↑ ↓

└───────┘

Delayed lines

info

Основа понимания D-trigger

Линия задержки. В задаче предоставлен компонент с задержкой в один tick.

Компонент с задержкой «1 такт» не отдаёт свой вход сразу, а только на следующий шаг симуляции.

tick = 0: вход = A → Delay1 хранит A, Delay2 хранит старое значение

tick = 1: вход = B → Delay1 выдаёт A, Delay2 выдаёт старое значение

tick = 2: вход = C → Delay1 выдаёт B, Delay2 выдаёт A

Синхронизация здесь нужна «логически», чтобы симулятор понимал, что значения обновляются только по тактам, а не мгновенно. Так как в реальном мире электроники, компоненты работают только по тактам.

Задача: Создайте цепь которая выводит свой собственный вход с задержкой в 2 такта.

Решение простое: последовательно два компонента с задержкой 1

Input → [Delay 1] → [Delay 2] → Output

Odd ticks

Нечетные такты.

Мы не дорускаем круговых зависимостей. Но есть одно исключение.

Линия задержки может зависеть от собственного входа. Это потому, что её вход не влияет на остальную схему до следующего такта.

Квадратные контакты в игре никогда не влияют на вывод в тот же такт. Поэтому они никогда не вызывают круговых зависимостей.

Задача: Выведите 0 для четных тактов и 1 для нечетных тактов.

Мы хотим сигнал, который чередуется каждый такт:

- Есть компонент Delay на 1 такт → он помнит прошлое состояние

Odd ticks (www.falstad.com/circuit)

Bit Inverter

Битовый инвертор

Задача: Имеем два входа: invert и value. Когда вход invert 1, выведите обратное от value. Иначе, просто выведите value как есть.

Найти решение которое соответвует такой таблице истинности. Это напоминает поведение XOR

| i/v | 0 | 1 |

|---|---|---|

| 0 | 0 | 1 |

| 1 | 1 | 0 |

Bit Switch (tri-state buffer)

tip

Разблокирует:

- переключатель на 1 бит

S - 8-ми битный

SWC

important

Главная цель битового переключателя (Bit Switch / Tri-state) - дать возможность нескольким источникам делить одну линию, не вызывая короткого замыкания к.з. (в Falstad → singular matrix)

A ─┐

├─── BUS

B ─┘

Если компоненты выдают разные значения по одному и тому же проводу, возникает ошибка (к.з.). Однако у некоторых компонентов выходные контакты могут иметь состояние выхода Z (high-impedance), и они вообще не выдают сигналы, когда компонент не активен,т.е. Z состояние это не просто низкий сигнал LOW/pull-down, а имеено электрическое отключение выхода/обрыв линии. Это относится и к компоненту Bit Switch.

important

На практике, состояние Z применяется в шинах (the bus)

REG0 ──┐

REG1 ──┼─── BUS ──► ALU

REG2 ──┘

У Bit Switch выход “Z” — это значит:

- когда switch выключен → он НИЧЕГО не выдаёт (провод “в воздухе”)

- когда switch включен → он пропускает вход на выход

Поэтому несколько Z выходов можно соединять в один провод, если гарантировано, что включён только один из них.

important

Bit Switch по сути это управляемый буфер с тремя состояниями

| Enable | In | Out |

|---|---|---|

| 0 | X | Z (отключён) |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

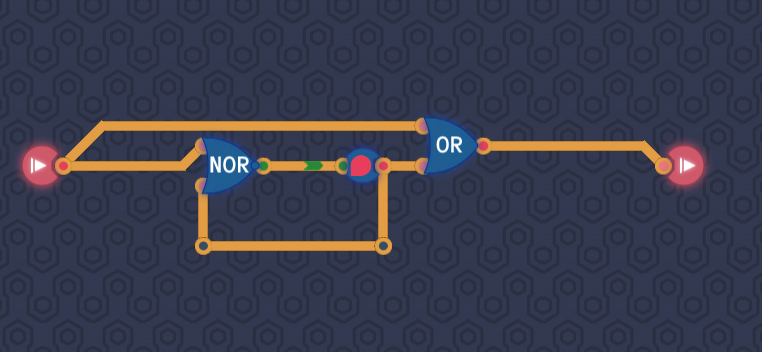

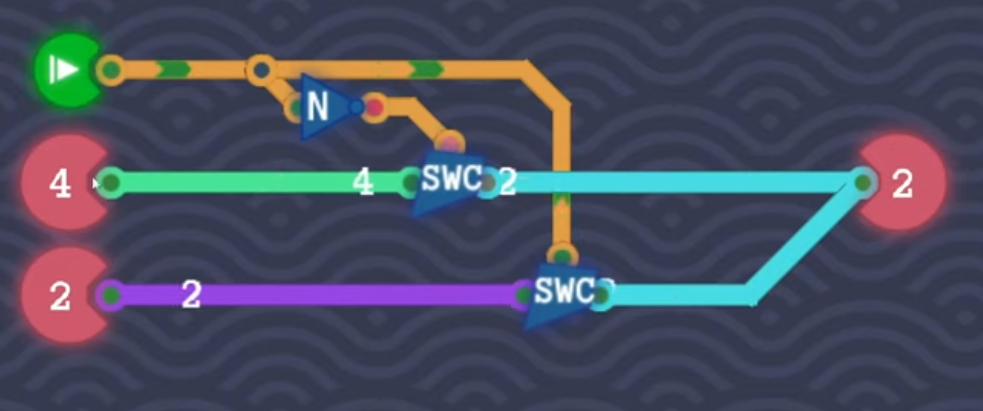

Задача: Собрать gate XOR используя два переключателя switch и два gate NOT

- Один switch отвечает за случай A=1, B=0

- Второй switch — за A=0, B=1

- Их выходы соединены в один провод

- Одновременно они никогда не активны

| XOR | 0 | 1 |

|---|---|---|

| 0 | 0 | 1 |

| 1 | 1 | 0 |

(A AND !B) ─▶ buffer ┐

├──▶ OUT

(!A AND B) ─▶ buffer ┘

Из 8 штук битовых переключателей, можно сконструировать 8-ми битный переключатель самостоятельно.

Circuit Simulation: gate XOR

(Собрать gate XOR используя два переключателя switch и два gate NOT)

Если учитывать состояние Z, то при A=1, B=1 оба tri-state буфера отключены, и линия оказывается в состоянии Z — никто не тянет её ни в 0, ни в 1. Чтобы в этом случае получить 0, добавляют pull-down — подтяжку к нулю по умолчанию. Тогда при отсутствии активных драйверов (Z) выход принимает значение 0 по умолчанию.

Bit Switch (www.falstad.com/circuit)

Circuit Simulation: Bit Switch

(также часто называют "pass transistor logic", "передающий транзистор" или "ключ")

В CircuitJS нет прямого “tri-state buffer” как в игре Turing Complete.

Но есть аналог из реальной электроники для правильного моделирования состояния Z:

- Управляемый ключ на N-MOSFET (или NMOS):

- Сток (Drain) и Исток (Source) подключаются в разрыв вашей сигнальной линии

- Затвор (Gate) — это управляющий вход

- Принцип: Режим ключа предполагает заземлить подложку Body/Bulk, что бы диод не открылся когда на стоке напряжение выше, чем на истоке,что лишит нас возможности управлять затровором Gate. Когда на затвор Gate подается высокий уровень (логическая 1, напряжение, близкое к Vdd), транзистор открывается и проводит сигнал между стоком Drain и истоком Source. Когда на затворе низкий уровень (0), транзистор закрывается и разрывает цепь.

- Недостаток: пороговые потери (Threshold Voltage, Vth) на преодоление барьра открытия транзистора, что снижает выходное напряжение, например если HIGH был 5 Вольт, то на выходе 3.5 Вольт, что в каскаде т.е. дальнейшее использование сигнала HIGH с выхода уже невозможно!

- Transmission Gate (Analog Switch)

- Он состоит из параллельно соединенных N-MOSFET и P-MOSFET, управляемых инверсными сигналами.

- Когда ключ открыт, он отлично передает как 0, так и 1 без потерь напряжения.

- Трёхстабильный буфер (Tri-state buffer)

- По сути, трёхстабильный буфер — это "цифровая" версия Transmission Gate с гарантированными уровнями 0V/5V на выходе.

Bit Switch NMOS,Transmission Gate,Tri-state buffer (www.falstad.com/circuit)

8 bit Switch and 8 bit Multuplexers (MUX) Tri-state buffer:

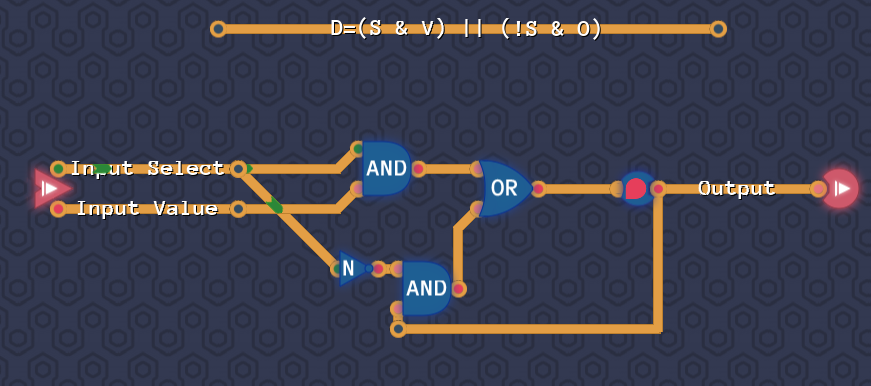

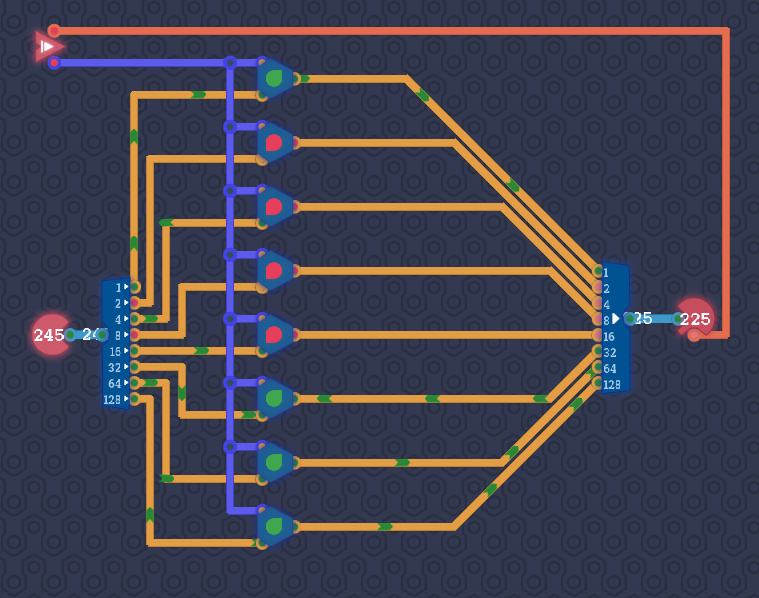

Input Selector

tip

Разблокирует 8-ми битный MUX / Мультиплексер

Multuplexers (MUX / Мультиплексер)

Задача: Если бит selector input установлен в 0, вывод Byte A, иначе вывод Byte B

Условие задачи (человеческим языком)

Есть:

- Byte A (8 бит)

- Byte B (8 бит)

- Selector (1 бит)

Нужно использовать Selector:

- если Selector = 0 → вывести Byte A и полностью игнорировать B

- если Selector = 1 → вывести Byte B и полностью игнорировать A

Мультиплексер для одного бита выглядит так: OUT = (A & !S) | (B & S)

| S | A | B | OUT |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 0 |

Input Selector 1 bit

Для байта — то же самое, но 8 раз, по одному биту.

Но есть уже готовый компонет, 8-ми битный переключатель

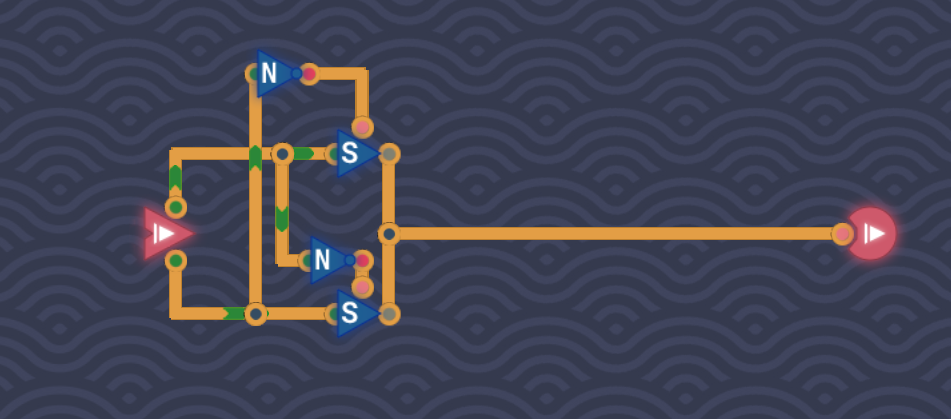

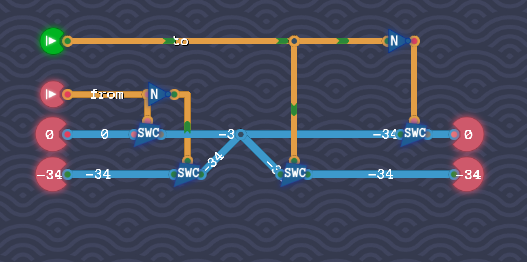

The Bus

Шина.

Задача: На этом уровне имеется 2 байтовых входа и 2 байтовых выхода.

Ваша задача — скопировать верные данные с одного из входов на один из выходов.

Первый входной бит определяет, с какого входа следует копировать данные. Второй входной бит определяет, на какой выход следует копировать данные.

Используйте переключатели, чтобы подключить входы к одному проводу.

шинный формирователь (3-state buffer)

EO=0, D=0, Output=Z

EO=0, D=1, Output=Z

EO=1, D=1, Output=1

EO=1, D=0, Output=0

Выход Q через один транзистор подсоединён к питанию, а через другой - к земле. Таким образом, если открыть верхний транзистор, то напряжение питания через него пойдет на выход. Если открывать нижний транзистор, то всё с выхода будет стекать на землю. В случае, когда оба транзистора закрыты, то выход Q ни к чему не присоединён, а значит это Z-состояние. И для полноты картины можно получить короткое замыкание (КЗ), если открыть оба транзистора. Управляющая логика из двух AND и одного NOT будет правильно открывать транзисторы, не допуская КЗ.

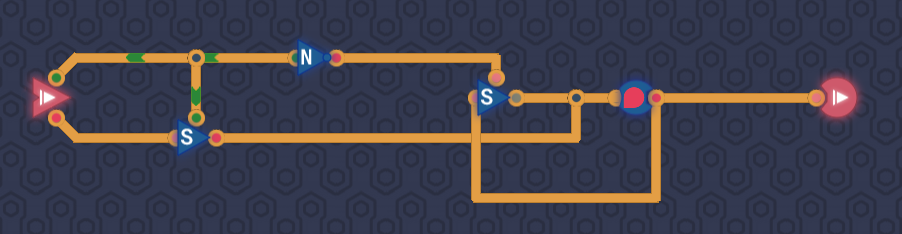

Saving Gracefully

Линия задержки позволяет нам использовать значение на 1 такт позже.

Нам нужно создать компонент, который позволит нам использовать значение, когда мы захотим, не важно на сколько тактов позже.

Такое значение называется сохранённым.

Задача:

На этом уровне 2 входа.

(Input Save) Только в случае если первый вход 1, обновите сохранённое значение.

(Input Value) Второй вход указывает какое значение нужно сохранить.

Всегда выводите сохранённое значение.

На этом уровне вам нужно использовать 1 линию задержки. Составьте таблицу истинности для того, что должно поступать на линию задержки. Рассматривайте вход линии задержки как выход для вашей таблицы.

Входами являются два входных сигнала уровня И выход линии задержки, поскольку выход играет роль во входном сигнале. В общей сложности у вас есть 3 «входа» для этой таблицы, что дает вам 8 комбинаций. Как только у вас будут требования к уровням в виде таблицы, решить задачу станет намного проще.

Реализовать поведение согласно таблице истинности:

| Input Save | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | 1 |

| Input Value | 1₁ | 1₂ | 0₃ | 0₄ | 0 | 1 | 0₅ | 1₆ | 1₇ | 1 | 0 | 0₈ | 0₉ |

| Output | 0₀ | 1₁ | 1₂ | 0₃ | 0₄ | 0₄ | 0₄ | 0₅ | 1₆ | 1₇ | 1₇ | 1₇ | 0₈ |

Эта задача — про запоминание (1-битная память), реализованную через одну линию задержки. Это однобитный регистр с разрешением записи (write enable).

- Input Save — управляющий сигнал

- Input Value — значение, которое можно сохранить

- Delay — задержка на 1 такт (это и есть «память»)

- Output — всегда должен быть сохранённым значением

Поведение:

- Если Save = 1 → обновить сохранённое значение (запомни Value)

- Если Save = 0 → оставить старое значение

- Выход всегда показывает то, что сохранено

Линия задержки не держит значение “сама по себе”. Она каждый такт перезаписывается. Т.е. у нее нет постоянного хранилища, она каждый такт перезаписывается своим же значением но при условии что мы не даем сигнал сохранить новое значение.

Мы не вычисляем Output напрямую. Мы вычисляем что подать на вход Delay на следующем такте.

Обозначим:

- S = Save

- V = Value

- O = OldIn (выход delay)

- D = вход DelayIn (то, что считаем)

Таблица истинности для того, что должно поступать на линию задержки. Рассматриваем вход линии задержки как выход для вашей таблицы.

| Save (S) | Value (V) | OldIn (O) | DelayIn (D) |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

Из таблицы напрямую получается логическая функция:

- при Save=0 → DelayIn = OldIn

- при Save=1 → DelayIn = Value

DelayIn = (Save AND Value) OR (NOT Save AND OldIn)

Circuit Simulation: Trigger

Классификация триггеров:

- Тип синхронизации

- синхронный - изменение состояния только по входу синхронизации CLK (clock). Позволяет избежать гонки данных, когда сингалы приходят в разное время.

- тип синхронизации высокий уровень CLK=1

- тип синхронизации низкий уровень CLK=0

- тип синхронизации передний фронт CLK=0

->CLK=1 - тип синхронизации задний фронт CLK=1

->CLK=0

- асинхронный - изменение состояния сразу в момент появляния данных (вход D)

- синхронный - изменение состояния только по входу синхронизации CLK (clock). Позволяет избежать гонки данных, когда сингалы приходят в разное время.

- Тип реализации

- однотактные (одноступенчатые)

- двухтактные (двухступенчатые) TT

- Тип функциональности

- RS-trigger (входы reset/set)

- JK-trigger

- D-trigger (с задержкой)

- T-trigger (с одним счетным входом)

Асинхронный RS-trigger

-

Реализация через gate NOR управление HIGH уровнем

- Операция Reset - установить выход Q=0, управляется HIGH уровнем т.е. R=1 S=0 Q=0

- Операция Set - установить выход Q=1, управляется HIGH уровнем т.е. R=0 S=1 Q=1

- Комбинация R=1 и S=1 запрещена, триггер в этом состоянии имеет неопределенное поведение. (Неопределенное состояние возникает при переходе с запещенного состояния в состояние хранения, тогда неопредленно что хранится)

Set Reset Q !Q состояние 0 0 пред. Q пред. !Q хранение (память) 0 1 0 1 reset 1 0 1 0 set 1 1 0 0 ошибка (запрещено) -

Реализация через gate NAND управление LOW уровнем

- Операция Reset - установить выход Q=0, управляется LOW уровнем т.е. R=0 S=1 Q=0

- Операция Set - установить выход Q=1, управляется LOW уровнем т.е. R=1 S=0 Q=1

- Комбинация R=0 и S=0 запрещена, триггер в этом состоянии имеет неопределенное поведение.

Set Reset Q !Q состояние 1 1 пред. Q пред. !Q хранение (память) 0 1 1 0 set 1 0 0 1 reset 0 0 1 1 ошибка (запрещено)

Синхронный RS-trigger

tip

В синхронной реализации RS-trigger, входы S/R не меняют свое расположение относительно реализаций через NOR или NAND, в отличии от асинхронных вариантов, где входы противоположны при сохранении позиций выходов Q/!Q

- вход CLK управляет временем для записи/чтения, т.е. при CLK=1 это режим записи, при CLK=0 режим чтения (запись заблокирована) в обоих реализациях

Реализация синхронного rs-trigger через gate NOR управление HIGH уровнем

-

Операция технические работы при CLK=0 мы изменяем состояние входов S/R триггера что-бы не попасть в неопредленное состояние

-

Операция Reset - установить выход Q=0, управляется HIGH уровнем т.е. CLK=1 R=1 S=0 Q=0

-

Операция Set - установить выход Q=1, управляется HIGH уровнем т.е. CLK=1 R=0 S=1 Q=1

-

запещенное состояние при одновременном снятии двух входов R и S. Например для реализации через gate NOR, переход с состояния R=1, S=1, CLK=1 на режим хранения R=0, S=0, CLK=1

Set Reset CLK Q !Q состояние ~ ~ 0 Q !Q память (чтение) 0 0 1 Q !Q память (чтение) 0 1 1 0 1 reset 1 0 1 1 0 set 1 1 1 0 0 ошибка

Реализация синхронного rs-trigger через gate NAND управление LOW уровнем

- Операция технические работы при CLK=0 мы изменяем состояние входов S/R триггера что-бы не попасть в неопредленное состояние

- Операция Reset - установить выход Q=0, управляется LOW уровнем т.е. CLK=1 R=0 S=1 Q=0

- Операция Set - установить выход Q=1, управляется LOW уровнем т.е. CLK=1 R=1 S=0 Q=1

- запещенное состояние при одновременном снятии двух входов R и S. Например для реализации через gate NAND, переход с состояния R=0, S=0, CLK=1 на режим хранения R=1, S=1, CLK=1

| Set | Reset | CLK | Q | !Q | состояние |

|---|---|---|---|---|---|

| ~ | ~ | 0 | Q | !Q | память (чтение) |

| 1 | 1 | 1 | Q | !Q | память (чтение) |

| 1 | 0 | 1 | 0 | 1 | reset |

| 0 | 1 | 1 | 1 | 0 | set |

| 0 | 0 | 1 | 1 | 1 | ошибка (запрещено) |

D-trigger

D-trigger (англ. Delay-задержка) может хранит один бит информации. Основное назначение D-триггеров - задержка сигнала, поданного на вход D.

- Вход D для данных DATA

- Вход C для синхронизации и управление моментом записи CLK

- Выход Q для выхода данных QUIT

- Выход !Q для выхода инферсии данных NOT QUIT

D-trigger не блокирует выход, т.е. данные DATA на его выходах Q и !Q есть всегда, а вот какие он выдает данные зависит от его типа срабатывания при записи.

Типы срабатывания (захват):

- Динамический т.е. срабатывание по фронту (edge-triggered/D-flip-flop) — запись (т.е. сохранение) происходит только при смене уровня, либо с LOW на HIHG либо с HIHG на LOW т.е. не сразу. Применяется в синхронных цифровых систем.

Типы срабатывание на фронте такта:

- передний фронт (rising edge, 0→1, LOW→HIGH) чаще всего

- задний фронт (falling edge, 1→0, HIGH→LOW)

- Статический т.е. срабатывание по уровню (level-triggered) — запись (т.е. сохранение) сразу и пока CLK = HIHG и тут же вывод этого значения (прозрачный режим, обычно называют «защёлкой», latch). Срабатывание по уровню указывает на то, что триггер сохраняет значение входа «DATA» в тот момент, когда сигнал на входе «CLK» достигает уровня HIHG. Современная электроника использует статический d-latch в ОЗУ (RAM) ячейках, дешифраторах

Схема динамического триггера D-trigger со срабатыванием по переднему фронту (rising edge, 0→1, LOW→HIGH). Комбинированный D-trigger собран на шести элементах И-НЕ (NAND) по схеме трех RS-триггеров. Двухступенчатый синхронный D-триггер с асинхронными сбросом и установкой.

tip

Обычно активные - LOW (чтобы избежать случайного срабатывания от помех). Такое поведение с управлением LOW режимом при реализации триггеров через gate NAND

Это означает захват по заднему фронту (falling edge CLK 1→0, HIGH→LOW)

D-latch

Статический т.е. срабатывание при наличии уровня т.е. прозрачный, реагирует сразу без задержки.

Цель D-latch (синхронной) в любой реализации — при активном такте (CLK=1) Q = D

Схема статического триггера D-latch со срабатыванием по уровню (level-triggered)

- основан на реализации синхронного rs-trigger через gate NOR управление HIGH уровнем

- недостаток, схема может работать только при коротких сингналах синхронизации.

D flip-flop

Динамический т.е. срабатывание по фронту.

- Захват по заднему фронту (falling edge CLK 1→0, HIGH→LOW)

- Когда CLK переходит c 0 → 1 (подьем), Master захватывает вход D (сохраняет),а Slave закрыт для записи.

- Когда CLK переходит с 1 → 0 (спад), Master закрывает вход D и его выход Q_m содержит предыдущее состояние входа D,а Slave теперь открывается и принимает предыдущее состояние D c Q_m и сразу выдает его на выход Q

- Захват по переднему фронту (rising edge CLK 0→1, LOW→HIGH )

- Reset синхронный, активный уровень переключения высокий (HIGH)

D Type Flip Flop (falling edge)

- Захват по заднему фронту (falling edge CLK 1→0, HIGH→LOW)

- Reset синхронный при CLK=0 и тоже по заднему фронту (falling edge CLK 1→0, HIGH→LOW) т.е. активный LOW

important

Для синхронной архитектуры регистров построенных на основе D-trigger, имеет решающее значение соблюдение очередности установки входных пинов CLK и Data. Если CLK и Data устанавливаются на одном тике то присутствует гонка данных, если CLK первым установился то новые Data не используются на этом тике, поэтому нужно соблюсти очередность, сперва Data потом CLK.

Positive Edge Triggered D Flip Flop

- Захват по переднему фронту (rising edge, 0→1, LOW→HIGH)

У стандартного D flip-flop:

- R = 0 → Reset (активен)

- S = 0 → Set (активен)

- R = 1, S = 1 → нормальная работа

То есть:

- R и S — асинхронные входы, активные нулём. Асинхронные Set/Reset = работают независимо от тактового сигнала CLK.

Реализация D-trigger (rising edge)

- Захват по переднему фронту (rising edge, 0→1, LOW→HIGH)

- С асинхронными Set/Reset управляемые LOW уровнем

- Режим записи CLK=1 S=1 R=1

- Запрещенный режим при CLK=1 S=0 R=0

Схема D-trigger rising edge (master slave)

- Задержка (delay) данных происходит в первом MASTER rs-trigger,а на следующем такте MASTER в режиме чтения отдает на вход SLAVE rs-trigger данные, которые сразу идут на выход так как это статические триггеры, но вместе они дают динамическое поведение.

- Реализация через gate NOR управление HIGH уровнем. Управление передним фронтом т.е. при переходе

CLK=LOW -> CLK=HIGH - Реализация через gate NAND управление LOW уровнем. Управление задним фронтом т.е. при переходе

CLK=HIGH -> CLK=LOW

- 74HC74 Двойной D-триггер с функциями установки и сброса от ON Semiconductors. Четырехканальные D-защелки данных 74LS75 от Texas Instruments.

- 74HC174 Шестиканальный D-триггер с функцией сброса от NXP.

- 74HC175 Четырехканальный D-триггер с функцией сброса от NXP. Восьмиразрядный D-триггер 74HC273 с функцией сброса от компании Texas Instruments.

- 74HC373 Восьмиканальные прозрачные D-триггеры данных с трехстабильными выходами от Texas Instruments.

- 74HC374A Восьмиканальный 3-состоятельный неинвертирующий D-триггер от ON Semiconductors.

Лучший практический вариант (индустриальный стандарт)

- Асинхронный assert, синхронный deassert

- То есть:

- Reset включается асинхронно

- Reset отпускается синхронно по CLK

Так же, D-триггер с динамическим входом C может работать как T-триггер. Для этого необходимо вход С соединить с инверсным выходом триггера /Q

Если на входе D поставить дополнительный двухвходовый элемент И и инверсный выход триггера /Q соединить с одним из входов элемента И, а на второй вход подать сигнал EI, то получим T-триггер с дополнительным разрешением по входу

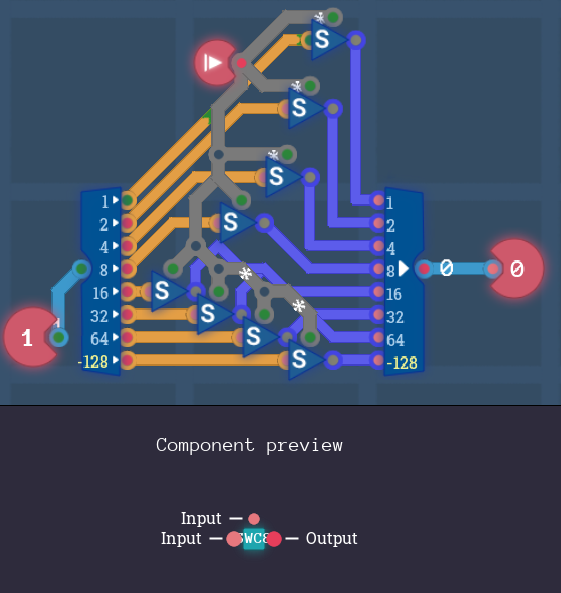

Saving Bytes

tip

Разблокирует компонент 1 ячейка памяти: Register 8 bit

Задача: Создать схему, которая может SAVE или LOAD байт.

Когда первый входной бит 1, LOAD память и пошлите её на выход.

Когда второй входной бит 1, SAVE входной байт.

У выхода есть активирующий контакт, активируйте его только если LOAD.

Это байтовая память на 1 ячейку (ОЗУ RAM (Random Access Memory) запись/чтение) с управлением:

Входы

- LOAD (бит) — читать сохранённое значение

- SAVE (бит) — записать новое значение

- DATA IN (байт) — что сохраняем

Выходы

- DATA OUT (байт) — сохранённое значение

- ENABLE (бит) — выход активен только при LOAD

Circuit Simulation: Saving Bytes

Необходимые компоненты:

Пример построение однобитной памяти с помощью D-триггеров (D Flip-Flop) - хранит 1 бит при тактировании.

Ячейка памяти через D-триггеры (D Flip-Flop). Это качественно и правильно для синхронного регистра, потому что запись происходит строго по фронту такта (строго в момент), нет проблем с гонками, как у защёлки/latch (пока Enable=1 - прозрачность, риск гонок). В реальных процессорах и ОЗУ ячейки строят на триггерах, а не на защёлках, именно для синхронности.

Компонент D-триггер (D Flip-Flop)

- вход

Dбит данных - вход

>тактирования - вход

Sасинхронный Set (часто обозначаетсяS, PRE, PSET— Preset). Когда на этот вход подаётся активный уровень (обычно 1), выход Q немедленно устанавливается в 1, независимо от тактового сигнала и входаD- Асинхронный - значит действуют мгновенно, без ожидания такта.

- вход

Rасинхронный Reset (обозначаетсяR, CLR, RST— Clear). При активном уровне на R выход Q немедленно сбрасывается в 0, независимо от такта иD - выход

Q - выход

!Qинверсный выход

Запрещённая комбинация. Если S=1 и R=1 одновременно для одного триггера — состояние выхода неопределённое (может быть 0, 1 или колебания). В реальных схемах это не допускается.

Логика LOAD/SAVE это логика WE/RD, реализуется через 2-to-1 Multiplexer (MUX)

WE — Write Enable (Разрешение записи)

- WE = 1 → запись новых данных в регистр из шины (BUS)

- WE = 0 → запись новых запрещена (старые данные записываются в регистр из Q выхода D-trigger, так как D-trigger предполагает по такту тактирования запись иначе может хранить мусор)

RD или OE — Read Enable / Output Enable (Разрешение чтения на общую шину)

- RD = 1 → чтение данных из памяти/регистра на общую шину

- RD = 0 → выход в высокоимпедансном состоянии (Z) на общую шину

CS (Chip Select) нужен для выбора конкретного устройства из множества на общей шине.

- Так как одновременно читать в шину может только один исчточник, то это можно обеспечить внешней логикой, не полагаясь на корретные инструкции.

- Роль уникального читателя на шину выполняет декодер адреса 3 на 8

Зачем нужен Multiplexer перед D-триггером?

У нас есть два источника данных для входа D:

- Внешние новые данные (когда SAVE=1)

- Текущие сохранённые данные с выхода Q (когда LOAD=1 — сохраняем старое)

Мультиплексор — это просто переключатель между двумя источниками.

- режим WE = 1 соответвует режиму SAVE=1, мы записываем новые данные в регистр с DataIn.

- режим WE = 0 соответвует режиму SAVE=0, мы не записываем новые данные, мы обновляем старыми

Реализация Multiplexer перед D-trigger не нуждается в Z состоянии. D-trigger не умееет хранить Z состояние. Поэтому в реализации Multiplexer нет буффера, достаточно простой логики (CMOS-логика):

D = (WE AND BUS) OR (NOT WE AND Q)WE = 1 (режим записи):

- D = (1 AND BUS) OR (0 AND Q) = BUS

- → На D идут данные с шины (новые данные).

WE = 0 (режим сохранения):

- D = (0 AND BUS) OR (1 AND Q) = Q

- → На D идёт текущее значение Q (старые данные).

Зачем нужен Tri-state buf на выходе с D-trigger? Так как такие регистры будут использоваться вместе, что предполагает общую шину данных для входа и выхода, то на выходе иногда потребуется Z состояние.

important

В один момент времени только одно устройство может выдавать данные на шину.

Но читать с шины могут многие одновременно. Но у нас декодер 3 на 8 жестко кодирует только однин адрес.

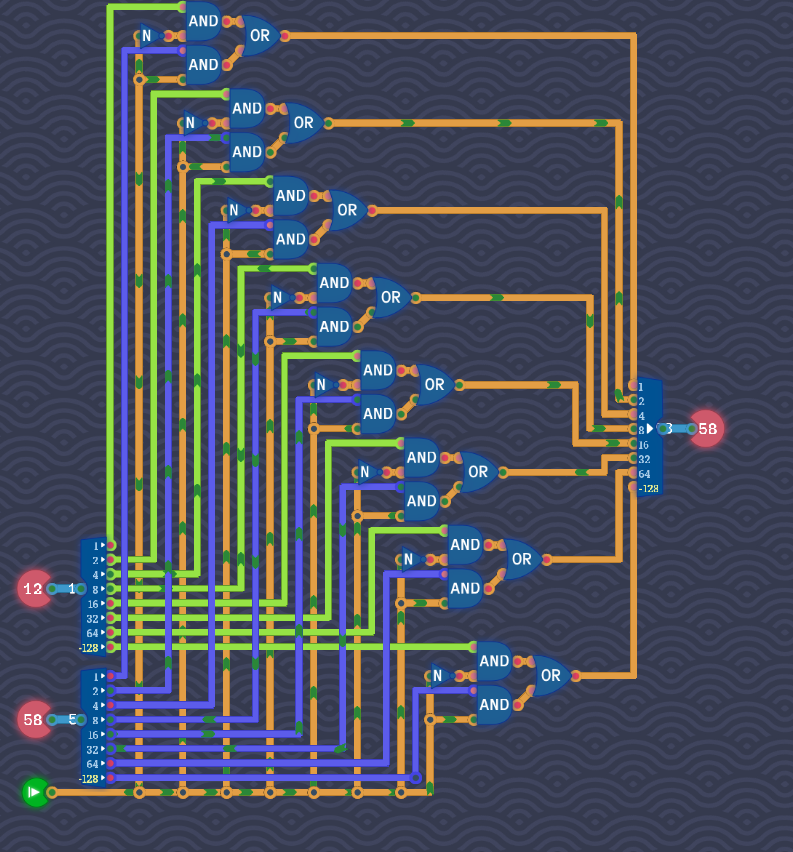

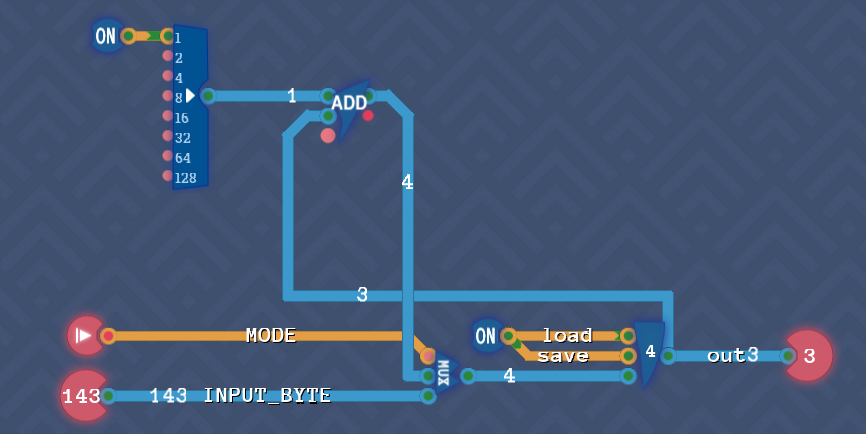

Counter

tip

Разблокирует компонент: 8-bit Counter

Задача: Создайте счётчик, который будет увеличиваться на 1 при каждом такте.

Кроме того, должна быть предусмотрена возможность перезаписи счетчика заданным значением.

Вам даны два входных параметра: бит (OPCODE) и байт (INPUT_BYTE).

Входной бит (OPCODE) должен переключаться между подсчетом и перезаписью значением байта.

Каждый такт:

- если OPCODE = 0 → counter = counter + 1

- если OPCODE = 1 → counter = INPUT_BYTE

Где:

- OPCODE (бит) — выбирает режим

- INPUT_BYTE — значение для перезаписи

- counter хранится в регистре (delay byte + обратная связь)

Есть 3 сущности:

- Регистр → хранит counter

- Инкрементер → считает counter + 1

- MUX → выбирает, что писать в регистр

MUX

- Если select = 0 → на выход идёт первый вход (counter)

- Если select = 1 → на выход идёт второй вход (INPUT_BYTE)

Counter (www.falstad.com/circuit)

tip

Этот уровень суммирует наши предыдущие полученные знания для построения счетчика PC (Program Counter счётчик)

Необходимые знания для построния счетчика:

- полусумматор

- полный сумматор

- 8-битное сложение

- линии задержки

- D-триггеры

- регистры

- SAVE / LOAD

- счётчик (логически)

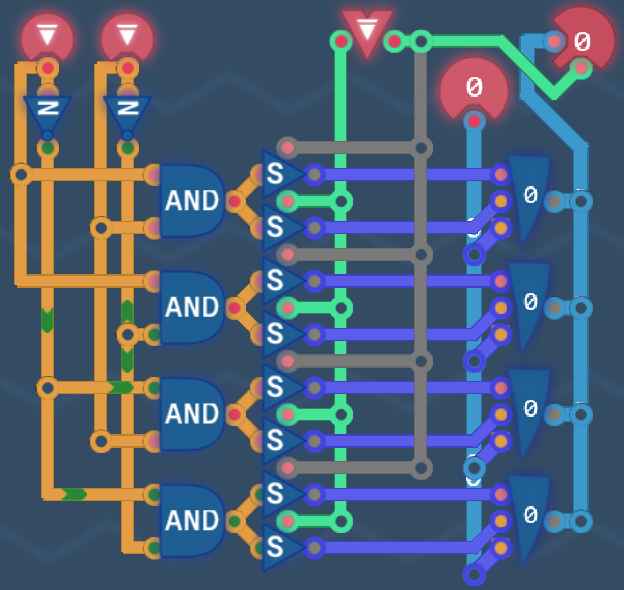

Little Box

tip

Разблокирует компонент памяти: 256 байтная ОЗУ RAM (Random Access Memory)

Можно ли уместить 4 байта в этом ограниченном пространстве?

Задача:

На этом уровне вы должны построить схему которая может [SAVE] или [LOAD] (показать (выдать) значение выбранного регистра на выход) из 4-х разных байтов памяти.

Вам даётся один быт который определяет нужно ли вам [LOAD]. Другой бит определяет нужно ли вам загружать [SAVE] и к нему прилагается значение.

Кроме того у вас есть 2 бита для адресас, что дает 4 комбинации, одна на каждый байт на этом уровне.

Для этого уровня вам, по сути, нужно создать четырехбайтовую оперативную память ((ОЗУ RAM (Random Access Memory) запись/чтение)) в ограниченном пространстве.

RAM 4×8 бит:

- 4 ячейки памяти

- каждая по 8 бит

- выбор ячейки по 2-битному адресу ADDR[1:0] — (00, 01, 10, 11)

- операции, декодер выбирает ровно один регистр:

- SAVE — при 1 записать байт в выбранную ячейку, при 0 не записывать

- LOAD — при 1 вывести байт из выбранной ячейки, при 0 не выводить

Для начала вам понадобятся четыре 8-битных регистра для независимого хранения и извлечения байтов.

- Соедините все выводы сохранения значений с входом, а все выводы вывода — с выходом.

- Подключите вывод загрузки к выводу разрешения выхода.

Далее соберите 2-битный декодер для активации одного из регистров за раз.

Наконец, используя восемь переключателей, создайте две шины, которые будут управлять выводами загрузки и сохранения регистров, и подключите их к соответствующим входам.

Соедините пары переключателей с соответствующими выходами декодера, и готово!

(Так же можно использовать компонент Switch вместо NOT + AND. Узел Switch можно использовать как логическое И, поскольку для его включения необходимо выполнение двух условий.)

2 bit decoder (2 to 4) нужен для выбора одного из четырех регистров

A B | addr

-------------

0 0 | 0001 D0

0 1 | 0010 D1

1 0 | 0100 D2

1 1 | 1000 D3

RAM 4×8 бит: